[12주 차] - 래치와 플립플롭 (Latch and Flipflop)

과목명 : 논리회로 실습(Logic circuit practice)

수업일자 : 2022년 11월 15일 (화)

1. Latch(래치) 회로

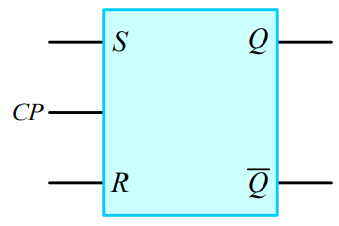

1-1. SR Latch

- NAND 게이트 래치 또는 NOR 게이트 래치가 존재합니다.

- SR 래치 회로에는 S(Set)와 R(Reset)로 표시된 입력 2개와 Q, Q'로 표시된 출력 2개가 존재하며 Q, Q'는 서로 보수가 되어야 정상 상태가 됩니다.

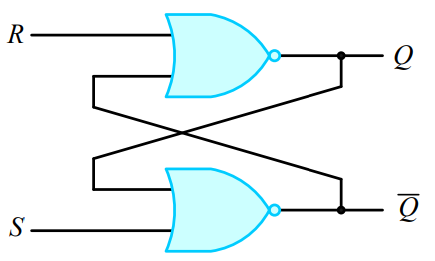

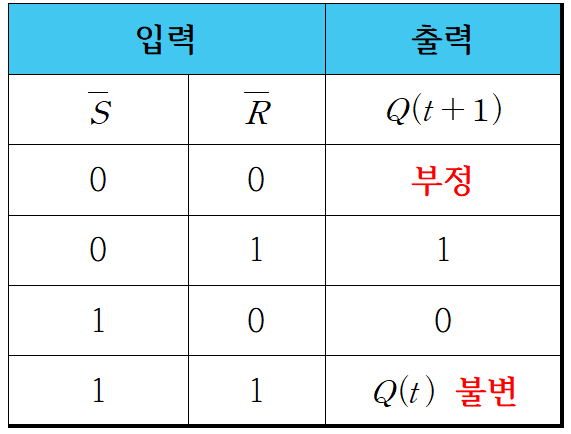

(1) NOR 래치

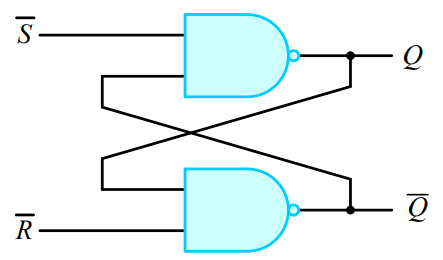

(2) NAND 래치

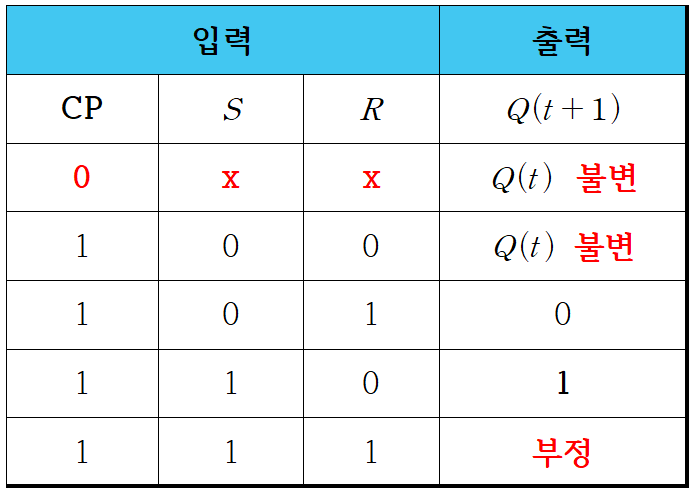

2. 클록형 래치

2-1. NOR를 이용한 클록형 SR 래치

- CP가 1일 때 동작합니다.

2-2. 클록형 D 래치

- SR 래치에서 원하지 않는 상태(S, R = 1)를 제거하는 방법을 고안하던 중 클록형 D 래치가 구현되었습니다.

- D 래치는 입력된 데이터가 그대로 저장되는 특성을 가집니다.

2-3. 클록형 JK 래치

(1) 여러 가지 특징

- SR 래치에서 S = 1, R = 1일 때 불안정한 문제를 해결하는 또 다른 방법은 JK 래치입니다.

- 가장 큰 특징은, J = 1, K = 1일 때 JK 래치의 출력이 이전 출력의 보수 상태로 변화한다는 것이 특징입니다.

- 여기서 J는 Set, K는 Reset으로 생각할 수 있습니다

(2) JK 래치의 문제점(Race problem)

- 레벨 트리거(Level trigger)에서 클록이 High 또는 Low로 유지되는 시간 동안 원하지 않는 입력의 변화가 발생할 수 있는데 이 때문에 저장값을 결정하지 못하는 현상이 JK 플립플롭에서 발생합니다.

- 쉽게 말하면 J = 1, K = 1일 때의 상황이 종료된 후 해당 메모리에 0인지 1인지 어떤 데이터가 들어있는지 알 수 없게 되는 상황이 발생하게 되며 이러한 문제를 레이스 문제(Race Problem)라고 합니다.

(3) JK 플립플롭의 특성표

3. 플립플롭(Flipflop)

3-1. 래치와 플립플롭의 차이

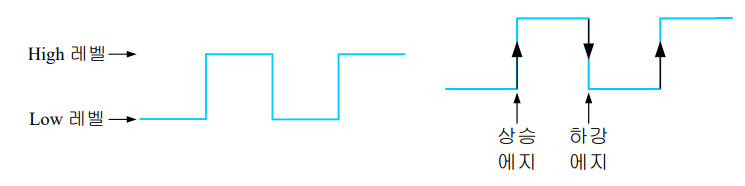

- 래치와 플립플롭은 순차 회로에서 한 비트의 정보를 저장하는 기억 소자이나 이들의 동작 방식은 트리거(Trigger) 방식에 따라 구분할 수 있습니다.

(1) 래치(Latch) - 레벨 트리거(Level trigger)에 대해 동작합니다.

(2) 플립플롭(Flipflop) - 에지 트리거(Edge trigger)에 대해 동작합니다.

(3) 레벨 트리거(Level trigger) - 상태 변수에 해당하는 현재 상황을 기준으로 동작하는 방식입니다.

(4) 에지 트리거(Edge trigger) - 상태 변수가 변화하는 순간을 기준으로 동작합니다.

(5) Rising edge 또는 Positive edge- 클록 펄스 값이 Low(0) → High(1)로 변화하는 순간을 의미합니다.

(6) Falling edge 또는 Negative edge- 클록 펄스 값이 High(1) → Low(0)로 변화하는 순간을 의미합니다.

- 위에서 잠시 언급된, 래치에서 발생하는 Race problem을 해결하기 위해 플립플롭을 사용하게 되었습니다.

- 에지 트리거를 사용하는 플립플롭은 논리 기호 CP에 삼각형 모양을 표시합니다.

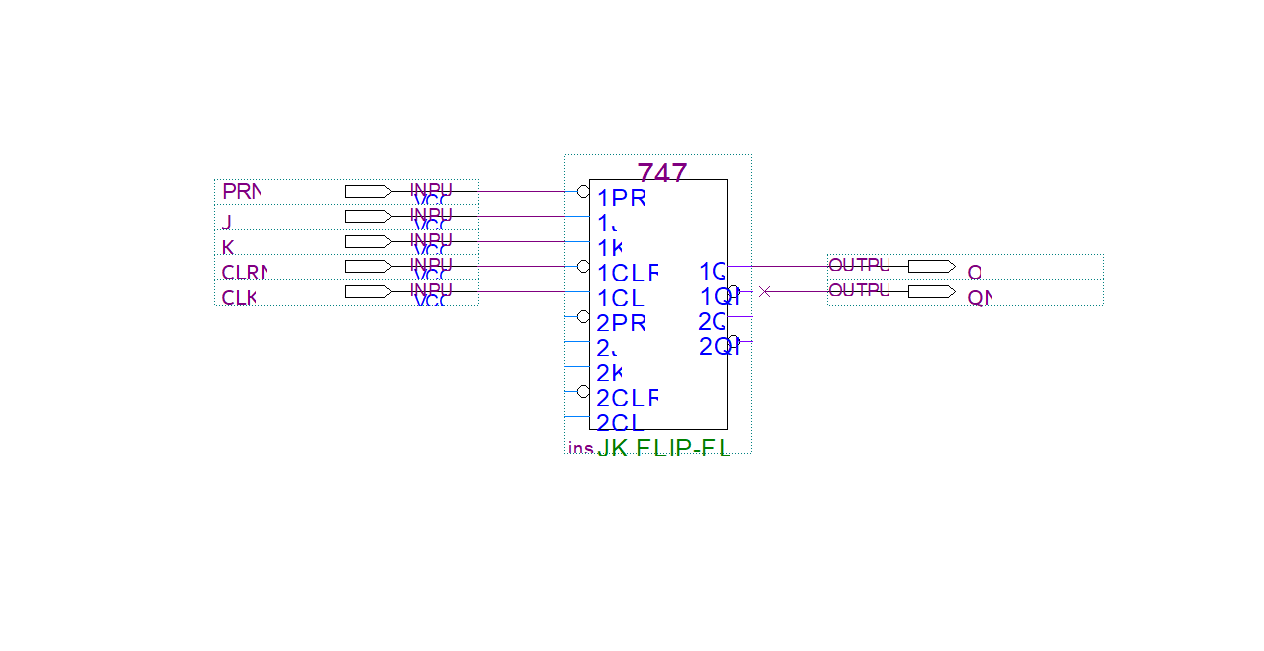

3-2. JK 플립플롭(7476)

- 7476 회로에는 하강 에지 트리거에서 동작하는 JK 플립플롭 2개가 내장되어 있습니다.

- 여기서 비동기 입력 신호는, 클록 펄스와 관계가 없으며 주로 초기값을 결정하고자 할 때 사용되는 신호입니다.

- PR은 비동기 신호로, 클록과 관계없이 1을 세팅하고, CLR은 0을 세팅합니다.

3-3. 7476 회로(JK 플립플롭)를 이용한 T 플립플롭

- JK 플립플롭의 J, K를 하나로 묶어서 아래와 같이 T 플립플롭을 구현할 수 있게 됩니다.

- 마찬가지로 하강 에지에서 동작합니다.

- T = 0이면 값이 변하지 않고 T = 1에서 츨력값이 보수 형태로 변화하게 됩니다.

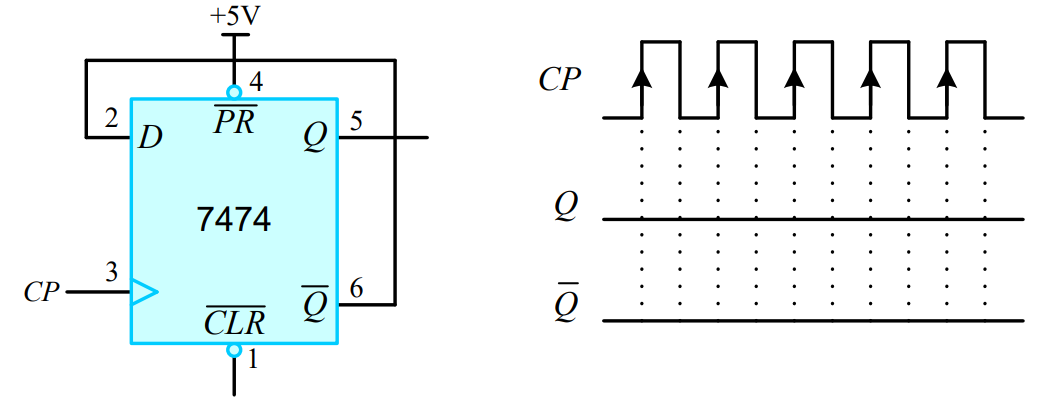

3-4. 7474 회로(D 플립플롭)를 이용한 T 플립플롭

- 7474 회로는 D 플립플롭 2개를 내장하고 있으며 7476과 마찬가지로 비동기 신호 PR, CLR 모두 존재합니다.

- 단 해당 플리플롭은 상승 에지에서 동작합니다.

- D 플립플롭의 출력 Q'를 입력 D에 연결하게 되면 T 플립플롭으로 동작하게 됩니다.

- D = 0에선 변화하지 않고 D = 1에서 출력값이 보수 형태로 변화합니다.

4. Simulation

4-1. 실험 & 문제

(1) 회로도 구성

(2) 회로도 Simulation

4-2.

(1) 회로도 구성

(2) 회로도 Simulation

- 학부에서 수강했던 전공 수업 내용을 정리하는 포스팅입니다.

- 내용 중에서 오타 또는 잘못된 내용이 있을 시 지적해 주시기 바랍니다.