과목명 : 컴퓨터 구조(Computer Organization & Architecture)

수업일자 : 2022년 11월 10일 (목)

< 입력/출력(Input/Output) chapter list>

(A) 외부 장치들

(B) I/O 모듈(Module)

(C) I/O 동작 기법

- 프로그램 I/O

- 인터럽트 구동 I/O

- 직접 기억장치 액세스(DMA)

(D) I/O 채널과 프로세서

1. I/O의 세 가지 동작 기법

1-1 프로그램 I/O (Programmed I/O)

- 프로세서와 I/O 모듈 사이에 데이터를 교환합니다.

- 프로세서가 주변 장치의 상태 감지, 읽기/쓰기 명령 전송, 데이터 전송 등과 같은 I/O 동작을 직접 제어합니다.

1-2. 인터럽트-구동 I/O (Interrupt-driven I/O)

- 프로세서가 I/O 명령을 보낸 다음에 I/O 모듈이 그 일을 완료하고 인터럽트를 보낼 때까지 다른 명령들을 수행합니다.

1-3. 직접 기억장치 액세스(Direct Memory Access, DMA)

- I/O 모듈과 주기억장치가 프로세서의 개입 없이 직접 데이터를 교환합니다.

2. 프로그램 I/O(Programmed I/O)

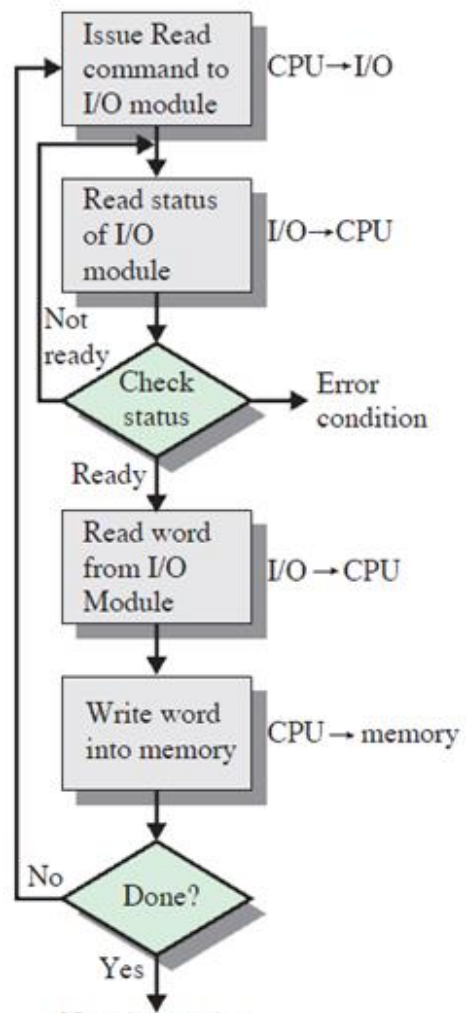

2-1. 프로그램 I/O의 동작

(1) CPU는 I/O 동작을 요청합니다.

(2) I/O 모듈은 동작을 수행합니다.

(3) I/O 모듈은 상태 비트를 세트합니다.

(4) CPU는 주기적으로 상태 비트를 체크합니다.

(5) CPU는 동작이 완료될 때까지 주기적으로 I/O 모듈의 상태를 검사합니다.

- I/O 모듈은 CPU에게 직접적으로 알리지 않고 인터럽트도 걸지 않습니다.

2-2. I/O commands

- 프로세서로부터 주소가 지정된 I/O 모듈이 받는 명령(Command)를 의미합니다.

(1) 제어

- 주변 장치를 활성화시키고 무엇을 해야 하는지 알립니다.

- ex) 자기 테이프 장치의 되감기 또는 다음 레코드로 이동

(2) 검사

- 모듈과 주변 장치들의 상태 조건들을 검사하는 것입니다.

- ex) 입출력 동작의 완료 여부, 오류 발생 여부 등

(3) 읽기

- I/O 모듈이 주변 장치로부터 데이터를 읽어서 내부 버퍼에 저장합니다.

- 프로세서는 I/O 모듈에게 특정 데이터를 데이터 버스에 싣도록 요구합니다.

(4) 쓰기

- I/O 모듈에게 데이터 버스로부터 데이터를 받은 후 주변 장치로 전송합니다.

2-3. I/O instruction

- I/O instructions의 경우 프로세서가 기억 장치에서 가져오는 I/O 관련 명령어입니다.

- 이에 따라 I/O command는 해당 instruction을 실행하기 위해 I/O 모듈로 보내는 명령을 의미하게 됩니다

- I/O command, I/O instruction은 1 : 1 사상 관계를 가지고 있습니다.

- 명령어(Instruction)의 형태는 외부 장치의 주소 지정 방식에 따라 결정됩니다.

- 각 장치들은 고유의 번호 또는 주소를 보유하고 있습니다.

I/O 모듈은 주소를 석하여 자신에게 보내진 명령어인지 판단하게 됩니다.

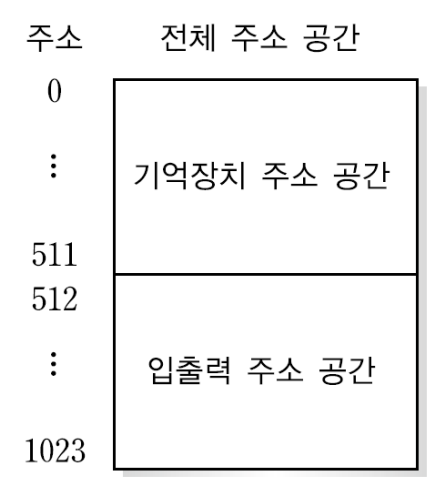

2-4. I/O 주소 지정 방식

- 프로세서 주기억장치, I/O 모듈이 한 개의 버스를 공유할 때 주소를 지정하는 방식입니다.

(1) 기억 장치 사상(Memory mapped I/O)

- 기억 장치와 I/O 장치들이 하나의 주소 공간을 공유하는 사상 방식입니다.

- I/O의 경우 주기억장치의 읽기 / 쓰기와 같습니다.

- I/O 장치를 액세스할 때 동일한 기계 명령어를 사용하게 됩니다.

(주기억장치의 접근 명령어를 폭넓게 선택할 수 있습니다.)

(2) 기억 장치 - 사상 I/O의 예시

- 키보드에서 한 바이트씩 데이터를 읽어 프로세서의 누산기로 보내는 프로그램

(3) 고립형 I/O (Isolates I/O)

- I/O용 별도의 주소 공간을 사용하는 사상 방식입니다.

- I/O와 주기억장치 선택선이 필요합니다.

- I/O를 위한 특정 명령어가 필요한 방식입니다.

(적은 수의 I/O 명령어를 사용합니다.)

(4) 고립형 I/O의 예시 - 특정 I/O 명령에 의해서 I/O 포트로 접근할 때

3. 인터럽트 구동 I/O(Interrupt driven I/O)

3-1. 프로그램 I/O의 문제점

- 프로세서가 I/O에 대해 처음부터 끝까지 관여해야 하기 때문에 프로세서의 대기 시간이 길어지며 이에 따라 전체 시스템의 성능 저하가 발생할 수 있는 문제점을 가지고 있습니다.

3-2. 인터럽트 구동 I/O의 정의와 특징

- 프로세서로부터 입출력 명령을 받은 I/O 모듈이 동작하는 동안, 프로세서가 다른 프로그램을 처리할 수 있도록 하는 입출력 동작 기법입니다.

(시스템의 효율성 증대되며 프로그램 I/O 입출력 동작 기법 보다 훨씬 더 높은 시스템 성능 기대 가능)

- I/O 모듈은 프로세서와 데이터 교환이 준비됐을 때, 프로세서에게 인터럽트(Interrupt)를 보내어 서비스 처리를 요구합니다.

- 그때 프로세서는 이에 따른 데이터 전송을 수행한 다음 이후 처리하던 일을 마저 수행하게 됩니다.

3-3. 인터럽트 구동 I/O의 동작 방식

(1) I/O 모듈의 읽기 관점

- 프로세서가 I/O 모듈로 읽기 명령을 보냅니다.

- I/O 모듈이 주변 장치로부터 데이터를 읽습니다.

(프로세서는 그동안 다른 일을 처리하고 있습니다.)

- I/O 모듈이 프로세서로 인터럽트 신호를 보냅니다.

- 프로세서가 데이터를 요구합니다.

- I/O 모듈이 데이터를 전송합니다.

(2) 프로세서의 읽기 관점

- 읽기 명령을 보냅니다.

- 명령을 보낸 후 다른 일을 처리하고 있습니다.

(명령어 사이클 마지막에 인터럽트 신호를 검사합니다.)

- I/O 인터럽트 발생

(문맥 저장(프로세서, PC) 후 인터럽트를 처리, I/O 모듈로부터 데이터를 읽어서 기억 장치에 저장합니다.)

- 이전 프로그램으로 다시 문맥을 복구합니다.

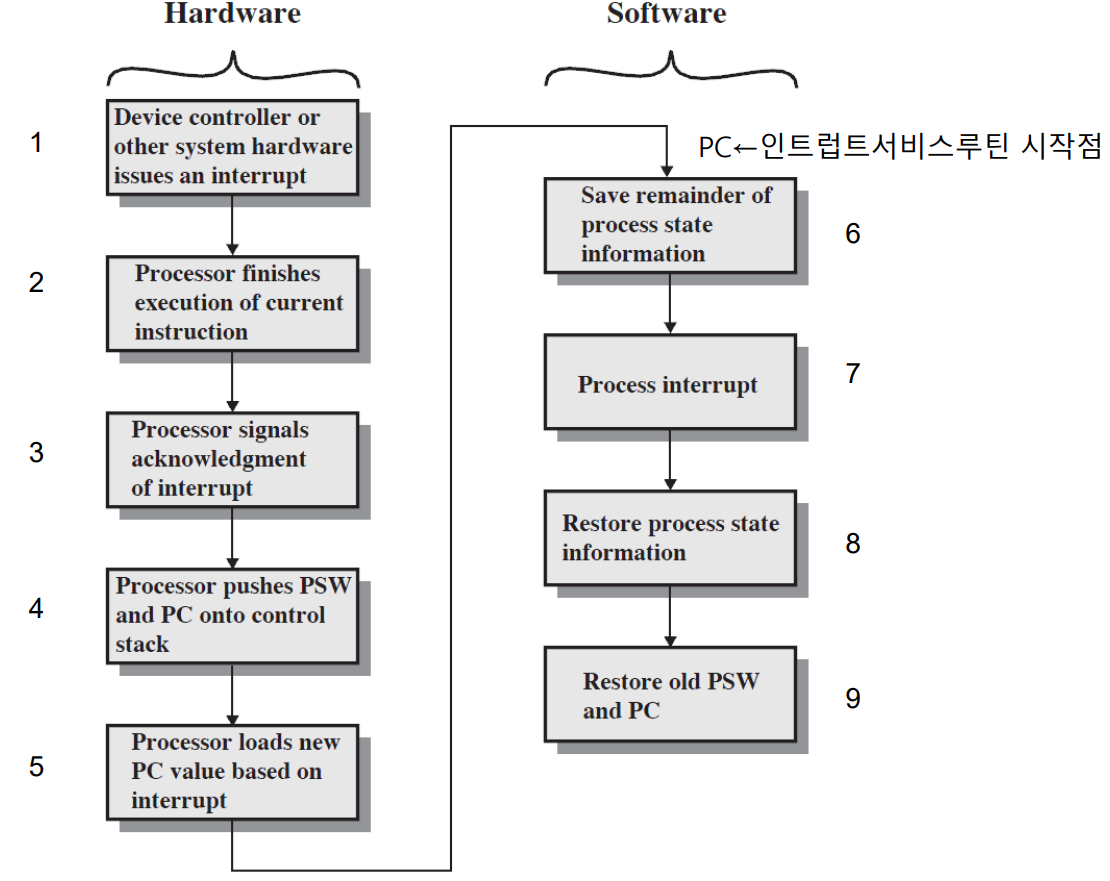

(3) 인터럽트 처리 과정

- 장치가 프로세서로 인터럽트 신호를 보냅니다.

- 프로세서는 인터럽트를 응답하기 전에 현재 실행 중인 명령어의 실행을 완료시킵니다.

- 프로세서는 인터럽트를 검사하고 인터럽트가 있다면 그 요구를 발생한 장치에 확인 신호를 보냅니다.

- 프로세서는 인터럽트 루틴으로 제어권을 넘길 준비를 합니다.

(프로그램 상태 단어(PSW)와 프로그램 카운터(PC) 내용을 스택에 저장합니다.)

- 인터럽트 처리 프로그램의 시작 주소를 PC에 저장합니다.(인터럽트 서비스 루틴의 시작)

- 프로그램 카운터는 인터럽트 서비스 루틴의 시작 위치를 가리키도록 갱신됩니다.

- 인터럽트 처리기가 인터럽트를 완료시킵니다.

- 인터럽트 처리가 완료되면, 저장된 레지스터의 내용들이 스택으로부터 인출되어 레지스터들로 복원됩니다.

- PSW와 프로그램 카운터의 내용을 스택으로부터 복원시킵니다.

(4) 인터럽트를 위한 기억 장치와 레지스터의 변화

(5) 인터럽트 I/O의 설계 이슈

- 다수의 I/O 모듈들이 있을 때 프로세서는 인터럽트가 발생한 장치를 어떻게 찾을 것인가? (인터럽트 발견 시)

- 다수의 인터럽트 발생 시, 프로세서는 어떤 인터럽트부터 처리할 것인가? (인터럽트의 우선 순위)

4. 인터럽트를 요구한 장치를 찾는 방법들

4-1. 다수의 인터럽트 선(Multiple interrupt lines)

(1) 각 I/O 모듈과 프로세서 사이에 인터럽트 요구(Interrupt request, INTR)선과 인터럽트 확인(Interrupt acknowledge, INTA)선으로 연결됩니다.

(2) 인터럽트를 요구한 장치를 찾기 쉽다는 특징이 있습니다.

(3) 하드웨어가 복잡하고 입출력 장치 수가 프로세서의 인터럽트 요구 입력 핀 수에 제한되는 특징을 가집니다.

(4) 쉬운 방법이면서도 확실한 방법입니다.

4-2. 소프트웨어 폴(Software poll)

(1) 프로세서가 모든 I/O 모듈에 접속된 Test I/O 선을 이용하여 인터럽트를 요구한 입출력 장치를 탐색하는 방법입니다.

- 임의의 입출력 모듈에서 인터럽트 요구가 INTR로 수신되면 프로세서는 특정 명령선(TEST I/O)을 활성화하고, I/O 모듈들의 주소를 순서대로 주소선에 내보냅니다.

- 어떤 I/O 모듈이 인터럽트를 요구하였다면, 자신이 선택되었을 때 응답합니다.

(2) I/O 모듈 검사 순서가 우선 순위입니다.

(3) 우선 순위의 변경이 용이하고 별도의 하드웨어가 필요하지 않으나 처리 시간이 오래 걸립니다.

4-3. 데이지 체인(Daisy chain, Hardware poll)

(1) 모든 I/O 모듈이 하나의 인터럽트 요구선(INTR)을 공유하고 있습니다.

(2) 인터럽트 확인 신호(INTA)를 위해 데이지 체인 형태로 연결되어 있습니다.

- 프로세서와 가까운 모듈의 우선순위가 높습니다.

(3) 동작 원리

- I/O 모듈이 인터럽트를 요구합니다.

- 프로세서가 확인 신호를 보냅니다.

- 인터럽트를 요구하지 않은 모듈은 다음 모듈로 통과합니다.

- 인터럽트를 요구한 모듈은 데이터 버스를 통해 인터럽트 벡터를 보냅니다.

(4) 벡터화된 인터럽트(Vectored interrupt) 구조를 가지고 있습니다.

4-5. 버스 중재(Bus arbitration)

- I/O 모듈은 인터럽트를 요구하기 전에 먼저 버스에 대한 사용권을 획득해야 합니다.

- 매 순간 하나의 모듈만이 인터럽트를 보낼 수 있습니다.

- 프로세서는 인터럽트를 감지하면 인터럽트 확인 신호를 활성화하여 응답합니다.

- 그 모듈은 데이터 선에 벡터를 올려놓습니다.

4-6. 인터럽트 벡터 테이블(Interrupt vector table)

- 인터럽트 서비스 루틴(ISR)의 주소를 저장한 테이블을 의미합니다.

- 운영체제가 관리하는 메모리 자료구조이며 인터럽트의 종류에 따라 인덱스(Index)가 저장됩니다

- 타이머 인터럽트, 벡터 테이블, 인터럽트 서비스 루틴(ISR)

4-7. 다중 인터럽트 요구 시 우선순위를 정하는 방법

5-1. 다수의 인터럽트 선

- 프로세서는 우선 순위가 높은 인터럽트 선을 선택합니다.

5-2. 소프트웨어 폴

- 검사하는 순서 → 우선 순위

5-3. 데이지 체인

- I/O 모듈이 연결된 순서 → 우선 순위

5. 직접 기억 장치 액세스(Direct Memory Access, DMA)

5-1. 프로그램 I/O, 인터럽트 구동 I/O의 단점

(1) I/O 전송률이 프로세서가 장치를 검사하고 서비스하는 속도에 의해 제한됩니다.

(2) 프로세서가 I/O 전송 관리를 위해 많은 시간을 소모합니다.

- 각 I/O 전송을 위해 많은 명령어들이 수행됩니다.

5-2. 직접 기억 장치 액세스(DMA)

- 기억 장치와 I/O 모듈 간의 데이터 전송을 별도의 하드웨어인 DMA 모듈(제어기)이 처리하며, 프로세서는 이 과정에 대해 전혀 개입하지 않는 방식을 의미합니다. ( 프로세서는 전송의 시작과 끝 부분에만 관여하게 됩니다.)

- 프로세서가 DMA 명령을 보낸 다음 프로세서는 다른 작업을 처리합니다.

5-3. DMA 동작

(1) 프로세서가 DMA 제어기로 다음 정보를 포함한 명령을 전송합니다.

- 제어선 : 연산 동작(쓰기/읽기) 지정

- 데이터선 : I/O 장치의 주소, 데이터가 읽히거나 쓰여질 주기억장치 영역의 시작 주소, 전송될 데이터 단어들의 수

(2) DMA 제어기는 프로세서로 버스 요구(Bus request) 신호를 전송합니다.

(3) 프로세서가 DMA 제어기로 버스 승인(Bus granted) 신호를 전송합니다.

(4) DMA 제어기가 주기억장치로부터 데이터를 읽거나 씁니다.

(5) 전송할 데이터가 남아있다면, (2)~(4)번 과정을 반복합니다.

(6) 모든 데이터들의 전송이 완료되면 프로세서로 INTR 신호를 전송합니다.

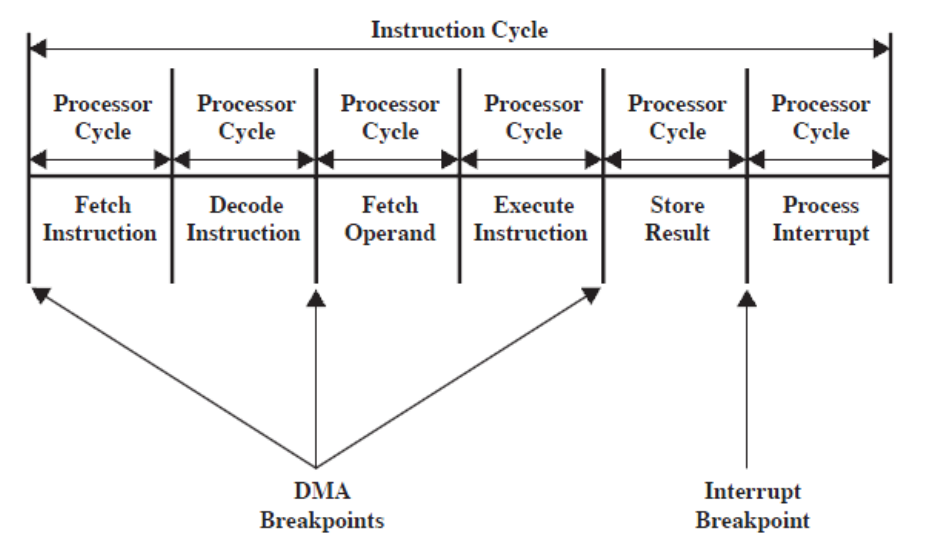

5-4. DMA 전송 사이클 스틸링(Cycle stealing)

(1) DMA 제어기가 데이터 전송을 위해서 버스 사이클을 사용합니다.

- DMA 모듈은 한 단어를 전송한 뒤에 버스를 프로세서에게 돌려줍니다.

(2) 해당 스틸링 방식은 인터럽트는 아닙니다.

- 프로세서가 상태 정보를 저장하지 않으며 한 버스 사이클 동안 잠시 정지합니다.

(3) 프로세서의 실행속도가 저하되나, 다중 단어 I/O 전송일 경우 인터럽트-구동 I/O, 프로그램 I/O보다 더 효율적입니다.

5-5. DMA를 구성하는 여러 가지 방법

(a) 단일 버스, 분리된 DMA

- 각 데이터 전송마다 시스템 버스를 2번씩 사용합니다. 비용은 적지만 비효율적인 단점이 있습니다.

(b) 단일 버스, 통합된 DMA - I/O

- DMA 모듈과 I/O 모듈 사이에 별도의 경로가 존재하며 시스템 버스를 사용하지 않습니다

- 하나의 데이터 전송을 위해 버스를 한 번만 사용합니다.

(c) I/O 버스

- I/O 모듈들은 I/O 버스를 통해 DMA 모듈에 연결되며 시스템 확장에 용이한 구성 방법입니다.

6. I/O 채널과 프로세서

6-1. I/O 기능의 발전 과정

(1) CPU가 주변 장치를 직접 제어

- 마이크로프로세서를 이용한 제어 장치에 적용되었습니다.

(2) 제어기 또는 I/O 모듈

- 프로세서가 인터럽트 없는 프로그램 I/O를 사용했습니다.

- 프로세서가 외부 장치 인터페이스 규격에 관여하지 않게 되었습니다.

(3) 2단계에서 인터럽트가 추가됨

- 프로세서가 I/O 동작이 수행되는 것을 기다리지 않으므로 효율이 향상됩니다.

(4) I/O 모듈이 DMA를 통하여 기억 장치를 직접 액세스

- 프로세서의 개입 없이 데이터 전송이 가능해졌습니다.

(5) I/O 모듈이 I/O 동작을 위한 특수 명령어 세트를 가진 프로세서를 포함

- 프로세서는 기억장치에 있는 I/O 프로그램의 수행을 I/O 프로세서에게 지시하고, 동작 전체가 완료된 시점에만 인터럽트됩니다.

(6) I/O 모듈이 자신의 지역 기억장치(Local memory)를 보유

- 프로세서의 개입이 최소화된 상태에서 많은 수의 I/O 장치들을 제어합니다.

6-2. I/O 채널의 특성

(1) DMA 개념을 확장

(2) I/O 채널은 I/O 명령어(Instruction)를 실행할 수 있는 능력을 가짐

- I/O 동작에 대한 완전한 제어권을 가지게 되었습니다.

(3) 프로세서가 I/O 명령을 실행하지 않고 I/O 채널 내에 있는 특수 목적용 프로세서가 해당 명령을 실행

- 프로세서가 I/O 채널에게 기억장치에 있는 프로그램을 실행하도록 지시함으로써 I/O 전송을 시작합니다.

(4) I/O 프로그램

- 외부 장치와 데이터 저장에 사용될 기억 장치 영역을 지정합니다.

- 우선 순위를 결정하며, 오류 발생 시 조치 사항을 지정합니다.

6-3. I/O 채널의 구조

(1) 셀렉터 채널(Selector channel)

- 여러 개의 고속 장치들을 제어하며 한 번에 한 장치와의 데이터 전송만을 제어하는 채널입니다.

- 데이터를 블록 단위로 전송합니다.

(2) 멀티플렉서 채널(Multiplexer channel)

- 동시에 여러 장치들과 I/O를 제어합니다.

- 서로 다른 전송률을 갖는 장치들과 효율적으로 데이터를 전송합니다.

- 데이터를 바이트 단위로 전송합니다.

- 학부에서 수강했던 전공 수업 내용을 정리하는 포스팅입니다.

- 내용 중에서 오타 또는 잘못된 내용이 있을 시 지적해 주시기 바랍니다.

'전공 수업 > 컴퓨터 구조(Computer Architecture)' 카테고리의 다른 글

| [13주 차] - 기계 명령어의 특성, 오퍼랜드, 연산의 종류 (0) | 2023.01.04 |

|---|---|

| [12주 차] - 컴퓨터 산술(Computer arithmetic) (2) | 2022.12.20 |

| [10주 차] - 외부 기억 장치 (2), I/O Module (0) | 2022.11.15 |

| [8주 차] - 내부 기억 장치 (2), 외부 기억 장치 (1) (0) | 2022.11.11 |

| [7주 차] - 캐시(Cache) 메모리 (2), 내부 기억 장치 (1) (0) | 2022.10.31 |

댓글