과목명 : 컴퓨터 구조(Computer Organization & Architecture)

수업일자 : 2022년 09월 22일 (목)

1. 벤치마크(Benchmark)

1-1. 정의

- 컴퓨터에서 벤치마크는 특정 오브젝트에 대해 일반적으로 수많은 표준 테스트와 시도를 수행함으로써 오브젝트의 상대적인 성능 측정을 목적으로 컴퓨터 프로그램을 실행하는 행위를 말합니다.

1-2. 벤치마크(Benchmark) 프로그램의 올바른 특징

- 고급 언어로 작성되며 서로 다른 기계들에서 호환성을 가져야 한다.

- 시스템 프로그래밍, 수치적 프로그래밍, 혹은 상용 프로그래밍과 같이 특정 종류의 유형에 대표적이어야 한다.

- 쉽게 측정될 수 있고, 널리 보급될 수 있어야 한다.

1-3. SPEC(System Performance Evaluation Corporation)

- SPEC 벤치마크의 경우 산업체 연합인 SPEC에 의해 정의되고 관리되는 벤치마크로써 SPEC 성능 측정들은 비교 및 연구 목적으로 널리 사용되고 있습니다.

- 벤치마크 모음집 중 하나인 *SPEC CPU2006은 대부분의 시간을 I/O보다는 계산 처리에 소모하는 응용들의 성능을 측정하는데 적절합니다.

*SPEC CPU2006 : 프로세서 - 중심 응용을 위한 산업 표준 벤치마크 세트이며 계산 처리를 많이 요구하는 응용들의 성능을 평가하기에 적합합니다.

- 참조 모델(Reference model)을 이용하여 각 벤치마크 프로그램에 대한 기본 시간을 정의합니다.

- 테스트되는 시스템에 대한 결과값들은 참조 처리 시간과 시스템의 처리 시간과의 비율로 보고됩니다.

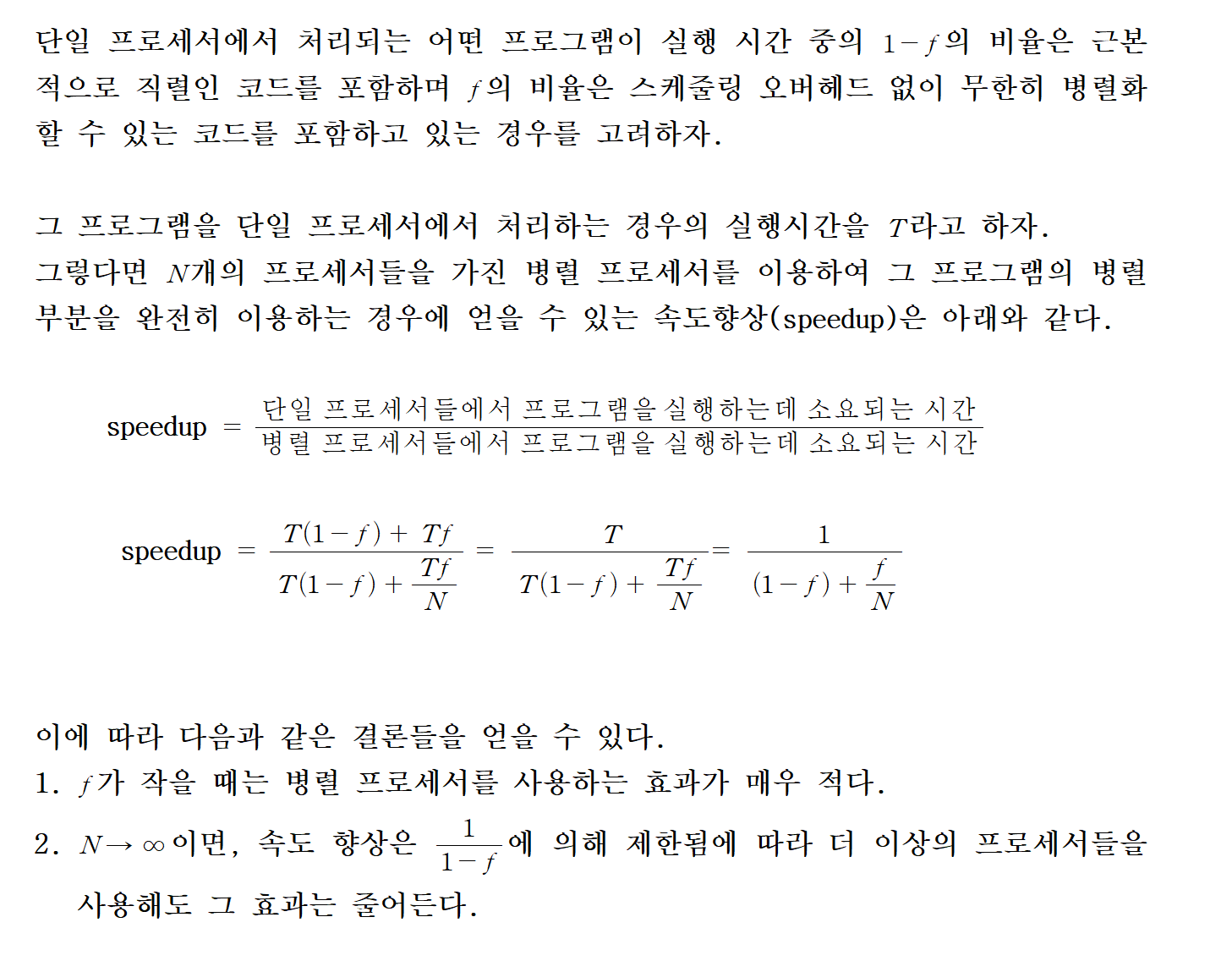

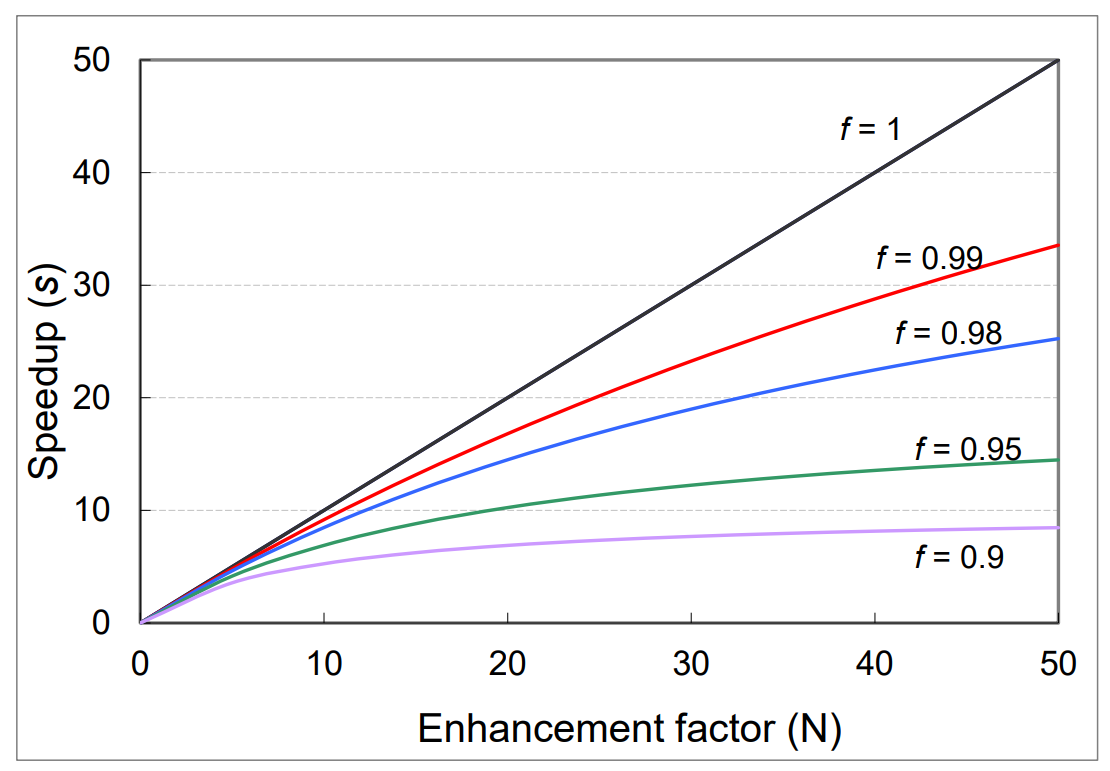

1-4. 암달의 법칙(Amdahl's Law)

- 시스템의 성능을 개선시키기 위해 병렬 프로세서들의 사용, 기억 장치 캐시 계층의 사용, 그리고 기억 장치 액세스 시간의 향상 및 기술 개선에 따른 I/O 전송율이 포함됩니다.

- 다만 이 모든 경우에서 어느 한 가지 기술이나 설계의 향상으로 성능 개선을 이룰 수 없다는 한계점을 암달의 법칙에 의해 명료하게 표현할 수 있습니다.

(1) 정의와 내용

- 암달의 법칙(Amdahl's Law)은 단일 프로세서에 비교하여 다수의 프로세서들을 사용한 프로그램의 잠재적 속도 향상에 대하여 다루고 있는 법칙입니다.

- 해당 속도 향상 그래프에서 볼 수 있는 것처럼, 위의 결론에 의해 f가 줄어들면 성능 저하는 급격하게 발생합니다.

2. Computer components

2-1. 최상위에서 본 컴퓨터의 구성 요소

(1) CPU(Central Processing Unit)

(2) 메모리(주 기억장치)

(3) I/O Devices

2-2. 폰 노이만 구조(Von Neumann Architecture)

- 폰 노이만 구조는 다음과 같은 세 가지 주요 개념들에 바탕을 두고 있는 구조입니다.

(1) 데이터와 명령어는 읽기와 쓰기가 가능한 기억 장치에 함께 저장된다.

(2) 기억 장치의 내용은 저장된 데이터의 형식에 관계없이 위치에 따라 주소를 지정할 수 있다.

(3) 명령어의 실행은 (별도의 수정이 없는 한) 한 개씩 순서대로 진행된다.

(4) 폰 노이만 구조는 프로그램 내장 방식이다.

2-3. 프로그램의 개념

(1) 하드와이어 프로그램(Hardwired program)

- 여러 부품들을 모아서 필요한 기능을 수행하도록 연결하는 과정을 프로그래밍의 한 형식으로 보는 것을 말하며 이 결과로 나타나는 프로그램은 하드웨어의 형태를 가지게 됩니다.

(2) 소프트웨어 프로그램(Software program)

- 범용 하드웨어를 가진 시스템은 데이터와 제어 신호를 받아서 그에 따라 다양한 결과를 생성할 수 있습니다. 이 경우에 개발자는 새로운 프로그램마다 별도의 하드웨어를 재구성할 필요 없이 새로운 제어 신호들을 제공해 주기만 하면 됩니다.

- 실제 프로그램은 실제로 여러 단계의 명령어들의 집합으로 구성되어 있고 각 단계마다 데이터에 대하여 산술 및 논리 연산이 진행됩니다.

- 위와 같은 방법을 위해 별도의 제어 신호의 집합이 필요하며 제어 신호 집합에 대하여 고유의 코드를 지정하고 해당 하드웨어에 코드를 받아들여 제어 신호를 발생시킬 수 있습니다.

- 개발자가 코드를 제공해 줌으로써, 하드웨어의 일부분이 해당 코드(명령어)를 해석하여 제어 신호를 발생시키게 됩니다. 이러한 새로운 프로그래밍 기법을 구분하기 위해 컴퓨터에게 특정한 동작 방법을 지시하기 위한 명령어들의 집합을 소프트웨어(Software)라고 정의하게 되었습니다.

2-4. 컴퓨터의 구성 요소와 그들 간의 상호 작용

3. 컴퓨터의 기능

3-1. 프로그램의 실행

- 프로그램은 기억 장치에 적재된 명령어들로부터 구성됩니다.

- 프로그램의 실행은 명령어 인출(Instruction fetch)과 명령어 실행(Instruction execution) 과정을 반복함으로써 이루어집니다.

- 프로세서는 프로그램 내의 명령어들을 수행하면서 실질적인 작업을 수행합니다.

3-2. 명령어 사이클(Instruction cycle)

(1) 정의와 특징

- 두 단계로 구성되며 기억장치로부터 한 번에 한 개씩 명령어를 읽어오고(인출) 각 명령어를 실행합니다.

- 한 개의 명령어 실행을 위해 필요한 과정을 명령어 사이클(Instruction cycle)이라고 부릅니다.

- 명령어 사이클은 인출 사이클(Fetch cycle)과 실행 사이클(Execution cycle)로 부를 수 있습니다.

(2) 명령어 인출(Fetch)과 실행(Execution)

(2-a) 프로세서가 기억 장치로부터 명령어를 인출한다

- 프로그램 카운터(Program Counter, PC) : 다음에 인출할 명령어의 주소를 가지고 있는 레지스터입니다. 프로세서가 명령어를 인출했다면 PC를 증가시켜 다음 명령어를 인출할 준비를 합니다.

(2-b) 인출된 명령어를 프로세서 내부 명령어 레지스터에 적재한다.

- 명령어 레지스터(Instruction Register, IR)

- 명령어는 바이너리 코드의 형태이며, 프로세서가 수행할 동작을 지정합니다.

(2-c) 프로세서는 명령어를 해석하고 그 결과에 필요한 동작을 수행할 수 있으며 이러한 동작들은 다음과 같은 네 가지로 분류할 수 있게 됩니다.

- 프로세서 <-> 기억 장치 : 프로세서와 기억 장치 사이의 데이터 전송

- 프로세서 <-> I/O : 프로세서와 I/O 사이의 데이터 전송

- 데이터의 처리 및 제어(Control)

- 데이터 처리의 종류로는 산술연산, 논리연산 등이 있으며, 제어(Control)의 경우 대표적으로 특정 명령어의 실행 순서를 변경시키는 제어가 존재합니다. 예를 들어 메모리의 주소 중 100번지에서 인출한 명령어가 다음 명령어는 200번지에 존재하는 명령어를 읽어오도록 지정하는 명령어였다면 PC를 200으로 세트함으로써 해당 사실을 기억하게 됩니다.

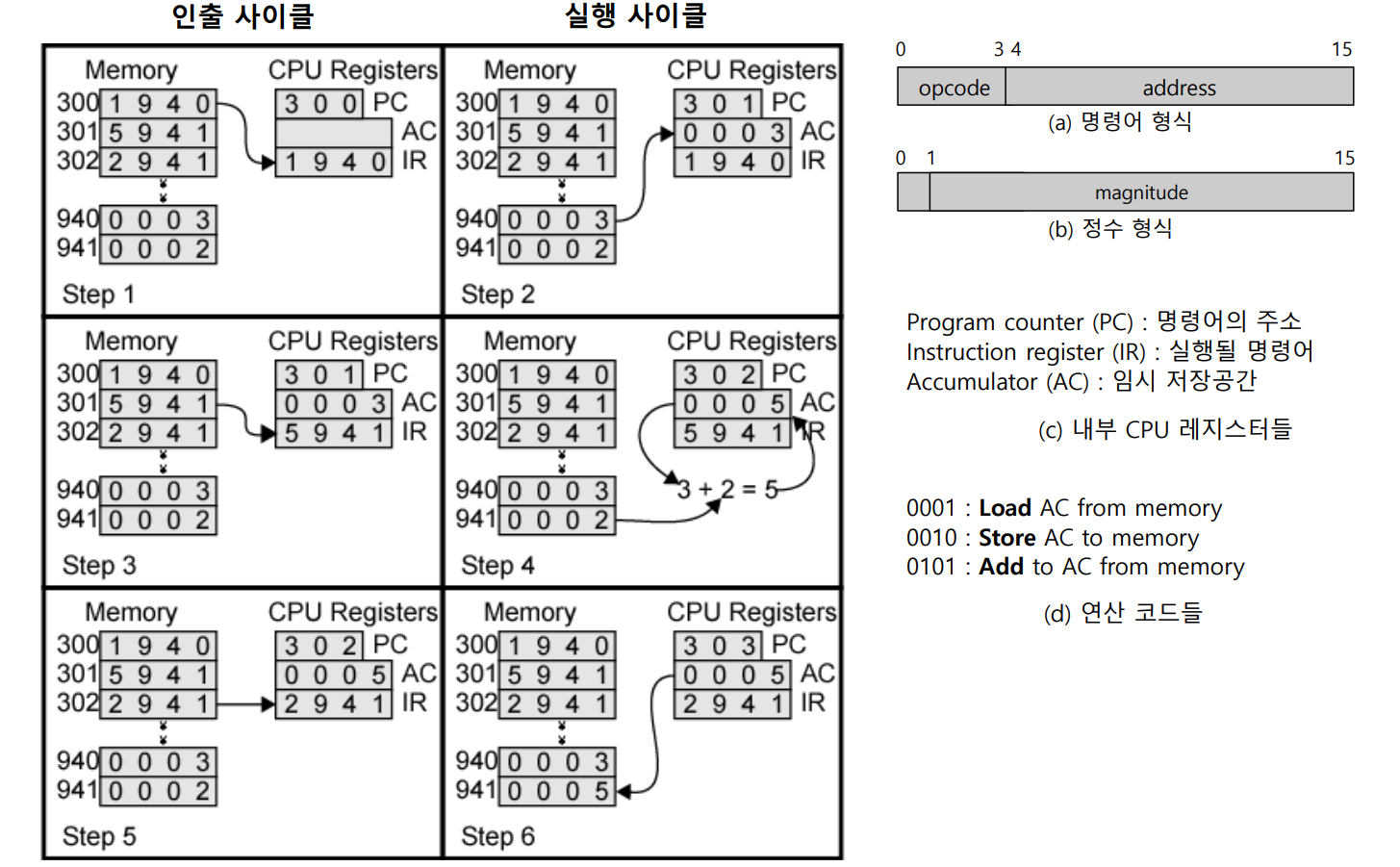

3-3. 프로그램 실행 예시

- 해당 과정은 세 번의 인출 사이클과 세 번의 실행 사이클이 각각 반복되면서 세 명령어들이 실행되는 예시입니다.

(1) PC(프로그램 카운터)가 첫 번째 명령어의 주소인 300을 가지고 있으며 해당 명령어는 IR(명령어 레지스터)로 적재되며 PC가 증가된다.

(2) IR에 있는 명령어의 첫 4비트는 누산기(AC)가 적재될 것이라고 알려주고, 나머지 12비트는 데이터가 적재되어 올 주소를 지정한다.

(3) 다음 명령어(5941)이 IR로 적재되고 PC가 증가한다.

(4) AC에 들어있던 내용과 941번지의 데이터가 더해지고 결과값이 AC에 저장된다.

(5) 다음 명령어(2941)가 302번지로부터 인출되고, PC가 증가한다.

(6) AC의 데이터가 메모리의 941번지에 저장된다.

3-4. PDP - 11 프로세서의 ADD B, A(A <-- A + B)의 처리 단계

(1) ADD 명령어 인출

(2) 기억 장치 A의 데이터를 프로세서로 읽어들인다.

(3) 기억 장치 B의 데이터를 프로세서로 읽어들인다. (단, A 번지의 내용을 잃어버리지 않기 위해 프로세서는 적어도 두 개의 레지스터를 보유하고 있어야 한다.)

(4) 두 값들을 더한다.

(5) 그 결과를 프로세서로부터 기억 장치 A에 저장한다.

3-5. 명령어 상태도(Instruction state diagram)

- CISC의 ADD B, A(A <-- A + B)

- 아래의 명령어 상태도는 위에서 언급되었던 기본 명령어 사이클에 모든 사항들을 추가하여 보다 자세하게 표현하고 있습니다.

- 명령어에 따라 어떤 상태는 거치지 않고 다음 상태로 건너뛰기도 하고 어떤 상태는 한 번 이상 거치기도 합니다.

- 명령어 주소 계산(Instruction address calculation)

다음에 실행될 명령어의 주소를 결정합니다. 일반적으로는 직전에 실행되었던 명령어의 주소에 일정한 수를 더합니다.

- 명령어 인출(Instruction fetch)

기억장치로부터 프로세서로 명령어를 읽어들입니다.

- 명령어 연산 / 해독(Instruction operation / decoding)

수행될 연산과 사용될 오퍼랜드의 형식을 결정하기 위해 명령어를 분석합니다.

- 오퍼랜드 주소 계산(Operand address calculation)

연산이 기억장치 혹은 I/O로부터 오퍼랜드를 필요로 할 경우, 그 오퍼랜드의 주소를 결정합니다.

- 오퍼랜드 인출(Operand fetch)

오퍼랜드를 기억장치로부터 인출하거나 I/O로부터 읽어들입니다.

- 데이터 연산(Data operation)

명령어가 지정한 연산을 수행합니다.

- 오퍼랜드 저장(Operand store)

그 결과를 기억장치에 저장하거나 I/O로 내보냅니다.

3-6. 인터럽트(Interrupt)

(1) 정의

- 인터럽트(Interrupt)란, CPU가 다른 프로그램을 실행하고 있을 때, I/O Devices나 하드웨어 등의 장치에 예외 상황이 발생하여 급하게 처리가 필요할 경우에 CPU에게 알려주어 처리할 수 있도록 하는 것을 의미합니다.

- 다른 모듈들이 프로세서의 정상적인 처리를 방해할 수 있는 메커니즘을 제공하는 것을 의미하기도 합니다.

(2) 인터럽트의 몇 가지 종류

- 프로그램 검사 인터럽트(Program check interrupt)

Division by zero, Overflow, Underflow나 기타 Exception이 발생한 경우이며 내부 인터럽트에 해당됩니다.

- 타이머에 의한 인터럽트

프로그램의 코드에 의해 특정 자원의 할당된 시간이 모두 끝난 경우이며 외부 인터럽트에 해당됩니다.

- 입출력 인터럽트(I/O interrupt)

입출력 장치 데이터가 전송을 요구하거나 전송이 끝나 다음 동작이 수행되어야 하는 경우 또는 입출력 데이터에 이상이 있는 경우에 해당되며, 외부 인터럽트입니다.

- 전원 이상 인터럽트(Power fail interrupt)

정전, 파워 이상 등의 문제로 발생할 수 있는 외부 인터럽트입니다.

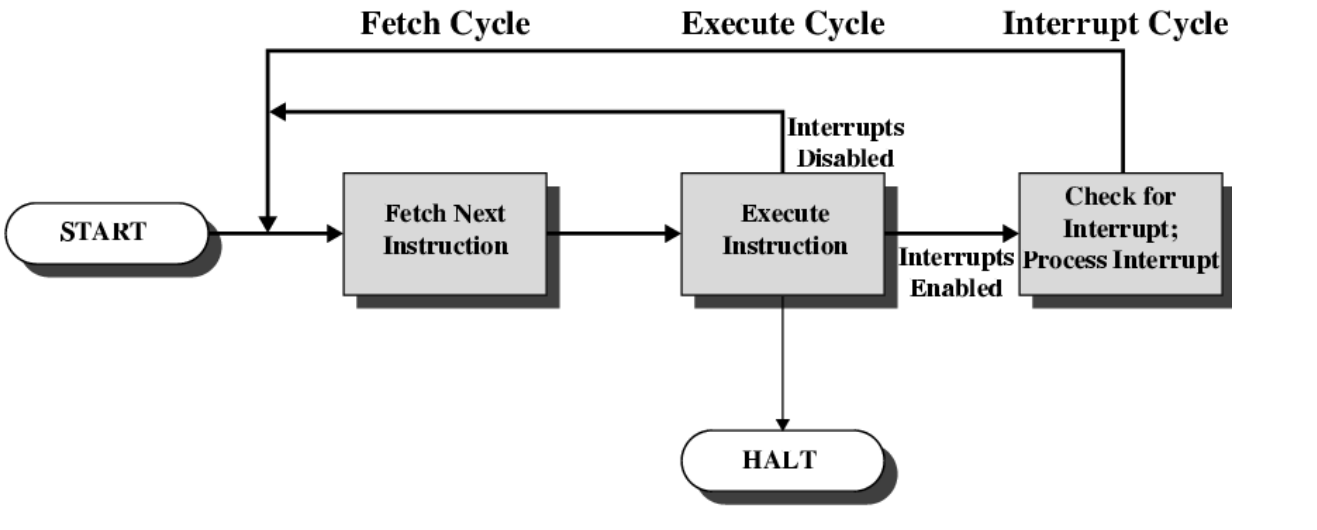

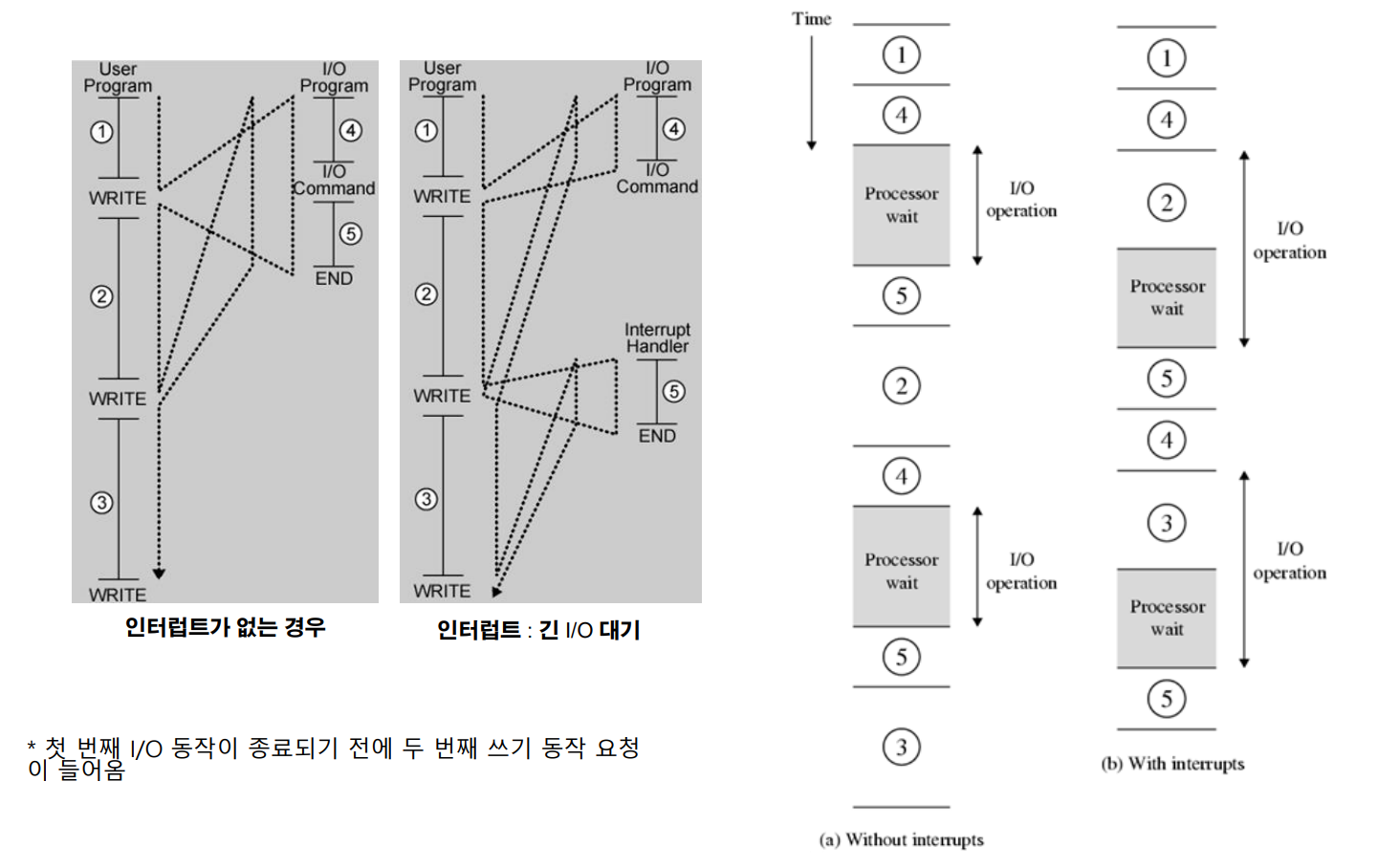

(3) 인터럽트를 포함한 명령어 사이클

- 만약 아래와 같이 인터럽트가 대기 중이라면 프로세서는 아래와 같이 동작합니다.

- 아래 내용은 인터럽트에 의한 제어권의 이동에 관한 내용입니다.

- 현재 프로그램의 실행을 중단하고 그 문맥(Context)를 저장합니다. 문맥이란 복귀 주소, 상태 정보를 담고 있는 데이터를 말하며 스택(Stack)에 저장됩니다. 이것은 다음 명령어의 주소(PC의 현재 내용) 및 프로세서의 현재 동작과 관련된 데이터를 저장하는 것을 의미합니다.

- PC에 인터럽트 처리기(Interrupt handler) 루틴의 시작 주소를 세트합니다.

- 프로세서는 명령어 인출 사이클로 돌아가서 인터럽트 핸들러의 첫 번째 명령어를 인출하여 인터럽트 발생에 대한 서비를 시작하게 됩니다.

- 인터럽트 핸들러 프로그램은 일반적으로 운영체제의 일부분이며 인터럽트의 성격을 결정하고 필요 동작을 수행합니다.

- 인터럽트 핸들러의 실행이 종료되고 이전에 실행이 중단됐던 프로그램을 다시 시작합니다.

(4) 인터럽트가 포함된 명령어 사이클의 상태도(State diagram)

(5) 인터럽트의 효용성

(A) 짧은 I/O 대기 상황의 경우

(B) 긴 I/O 대기 상황의 경우

(6) 다중 인터럽트의 처리 과정

- 순차적 인터럽트 처리

(a) 인터럽트를 처리하고 있는 중에는 추가적인 인터럽트가 불가능

(b) 발생한 인터럽트는 대기 상태로 있다가, 프로세서가 인터럽트 가능 상태가 되면 처리된다.

(c) 장점 : 간단한 로직으로 인터럽트들이 순차적으로 처리된다.

(d) 단점 : 상대적 우선 순위, 또는 시간적 위급성을 고려하지 않는 단점 발생

- 우선 순위에 따라 인터럽트를 처리하는 방법

인터럽트의 우선 순위를 결정하고 그 순위가 높은 인터럽트는 순위가 낮은 인터럽트보다 먼저 처리될 수 있도록 허용하는 것을 의미합니다.

- 학부에서 수강했던 전공 수업 내용을 정리하는 포스팅입니다.

- 내용 중에서 오타 또는 잘못된 내용이 있을 시 지적해 주시기 바랍니다.

'전공 수업 > 컴퓨터 구조(Computer Architecture)' 카테고리의 다른 글

| [6주 차] - 메모리(데이터) 참조 지역성, 캐시(Cache) 메모리 (1) (0) | 2022.10.18 |

|---|---|

| [5주 차] - 컴퓨터의 기능과 상호 연결 (2), 기억 장치 시스템의 특성 (0) | 2022.10.02 |

| [3주 차] - 컴퓨터 시스템의 성능 (1) (0) | 2022.09.19 |

| [2주 차] - 컴퓨터 시스템의 조직과 역사 (0) | 2022.09.12 |

| [1주 차] - 수업 개요 (0) | 2022.09.01 |

댓글