과목명 : 전자회로 설계(Electronic circuit design)

수업일자 : 2022년 11월 08일 (화)

1. MOSFET 공통 소스 증폭기

1-1. N 채널 MOSFET 공통 소스 증폭기 회로 구성

1-2. 바이어스(Bias)

1-3. 전압 이득

- 마이너스 부호는 입력 전압과 출력 전압의 위상이 서로 반대임을 의미합니다.

2. MOSFET 공통 소스 증폭기의 소신호 등가 모델

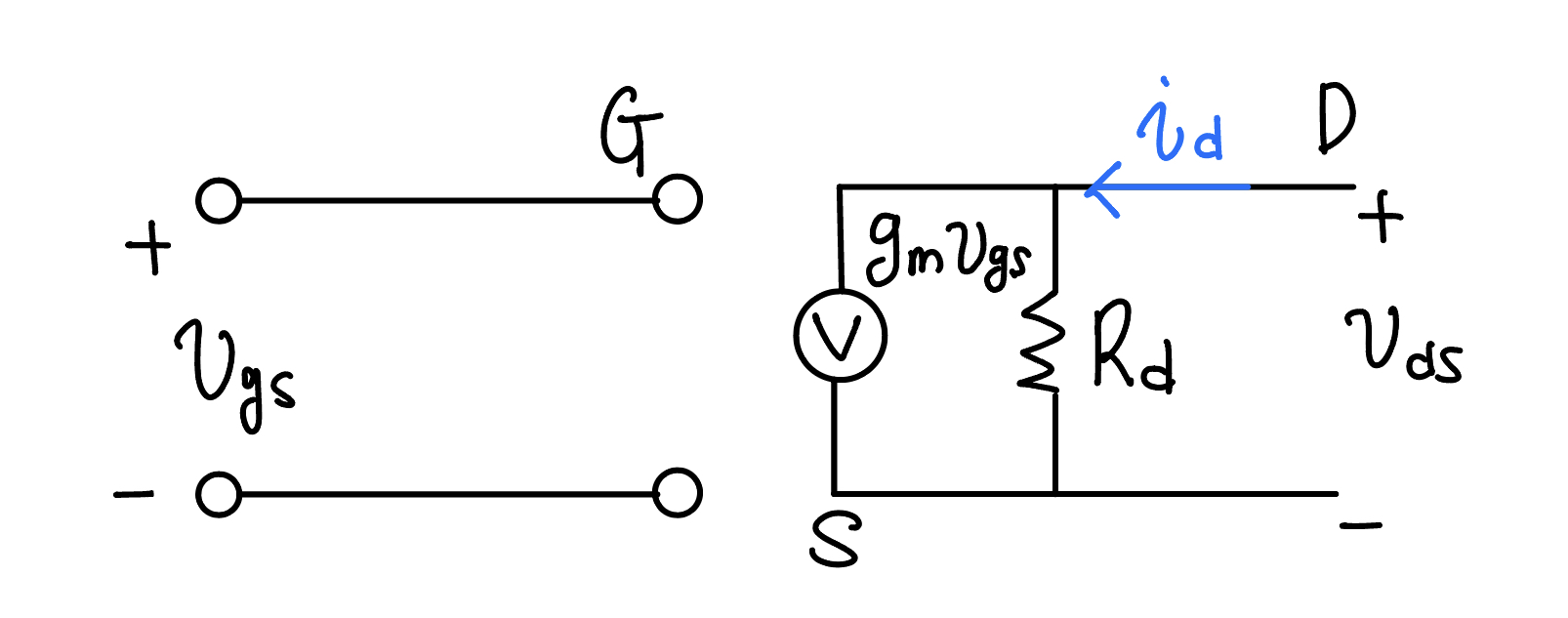

2-1. N 채널 MOFSFET 하이브리드 소신호 등가 모델

- 회로를 교류신호의 관점에서 분석하기 위해 해당 모델을 사용합니다.

2-2. 전달 컨덕턴스

- 입력 전압의 변화량이 출력 전류의 변화량에 얼마나 영향을 주는지에 대한 지표입니다.

(포화영역에서 동작하는 MOSFET는 게이트-소스 전압에 의해 제어되는 전압제어 전류원으로 동작)

- 전달 컨덕턴스는 전압 이득에 직접적으로 관련되는 중요한 파라미터입니다.

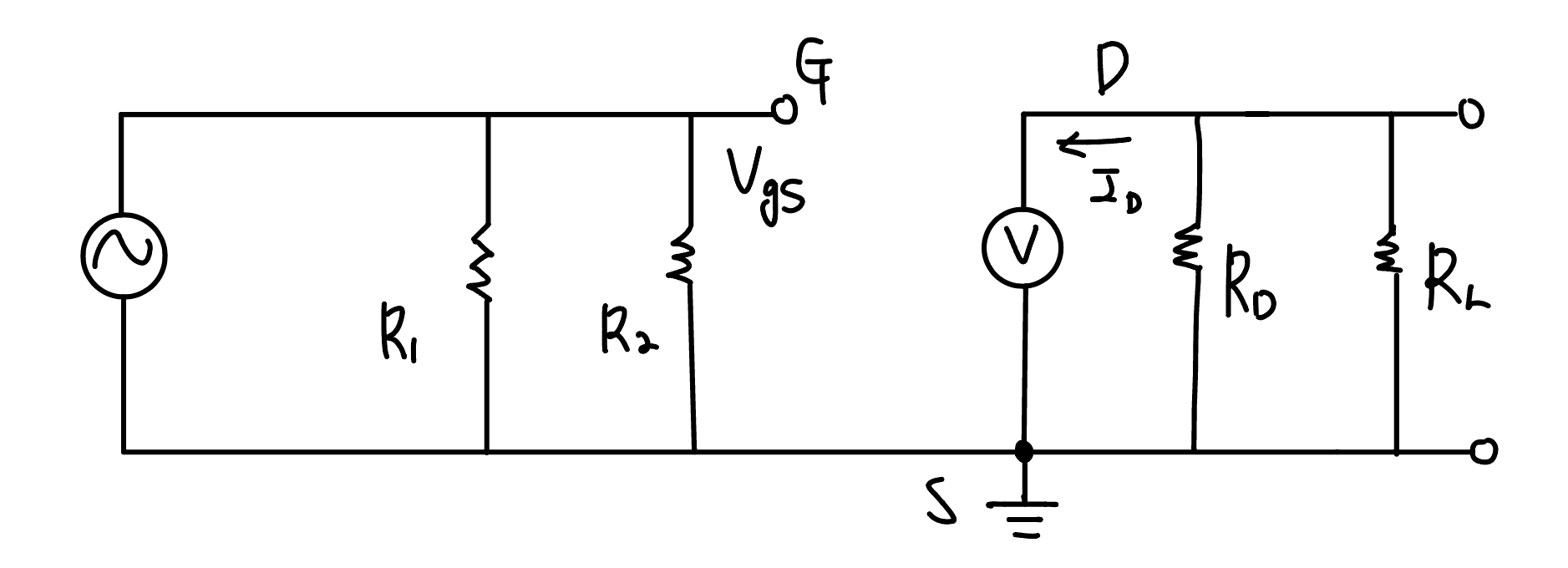

2-3. N 채널 MOSFET 증폭기의 소신호 등가 회로

(1) 부하저항이 1개인 경우

해당 회로를 아래와 같이 소신호 등가 회로로 변환할 수 있습니다.

(2) 부하저항이 2개인 경우

해당 회로를 아래와 같이 소신호 등가 회로로 변환할 수 있습니다.

3. DC 바이어스 해석, 소신호 등가 모델 해석

3-1. DC 바이어스 해석

3-2. 소신호 등가 모델 해석

- 학부에서 수강했던 전공 수업 내용을 정리하는 포스팅입니다.

- 내용 중에서 오타 또는 잘못된 내용이 있을 시 지적해 주시기 바랍니다.

'전공 수업 > 전자회로 설계' 카테고리의 다른 글

| [13주 차] - 연산 증폭기(OP Amp) 정의, 여러 가지 특성 (0) | 2022.11.23 |

|---|---|

| [12주 차] - 증폭기의 주파수 응답 특성 (0) | 2022.11.15 |

| [10주 차] - 증가형 MOSFET의 바이어스(Bias) 회로 (0) | 2022.11.02 |

| [8주 차] - 증가형 MOSFET의 전류-전압 특성 (0) | 2022.11.01 |

| [7주 차] - 공통 이미터, 컬렉터 트랜지스터 증폭기(Common Emitter, Collector Amplifier) (0) | 2022.10.11 |

댓글